“芯”榜样 | 周帅:心有热爱,行稳致远

编辑:集成电路学院 来源:集成电路学院 发布时间:2025-12-22 访问次数:11

“芯”榜样 |周帅:心有热爱,行稳致远

一、个人简介

周帅,2021级硕博连读生,电子信息专业

导师:谭年熊 教授

二、个人经历

(一)潜“芯”科研,硕果累累

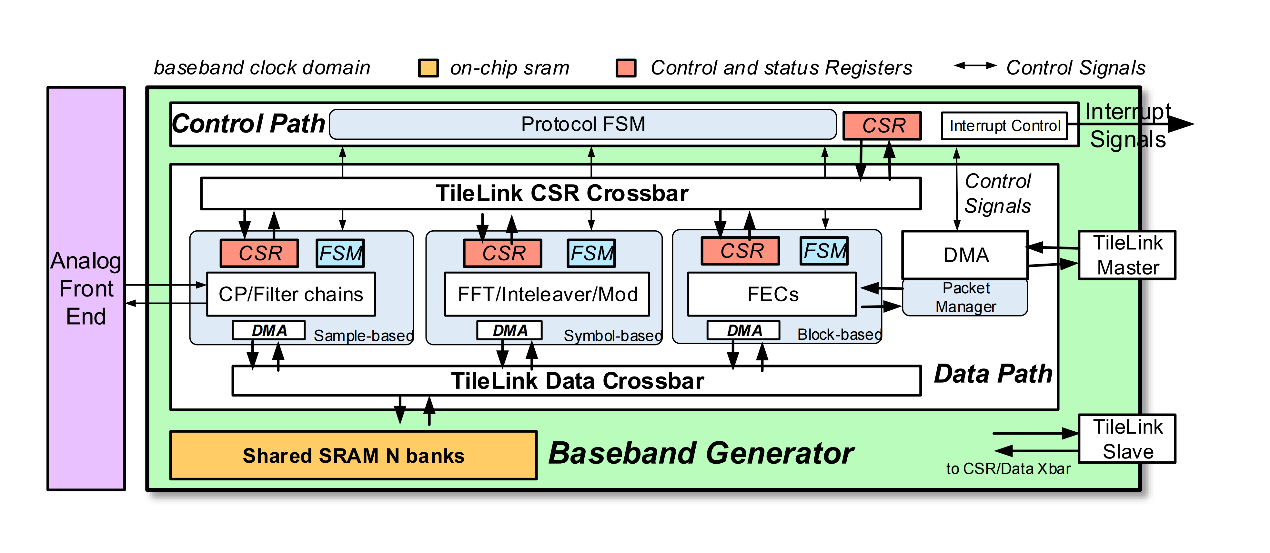

周帅同学研究方向主要聚焦于敏捷设计方法学与信号处理系统设计,致力于提升通信SoC系统的设计、验证与优化效率。具体包括面向能源物联网应用的可重构OFDM 处理器、参数化DSP模块生成、AI辅助设计验证、多层次设计空间探索等,实现了从通信协议到硬件实现的端到端敏捷开发框架。

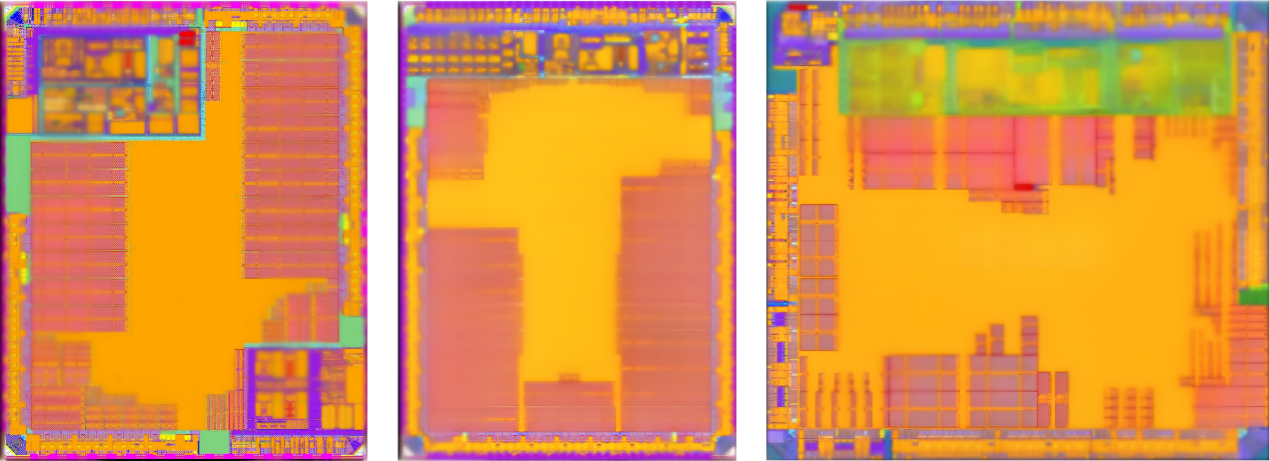

读博期间,他将学术理念和科研成果应用于企业一线项目,显著提升了芯片研发效率,同时缩短开发周期。实习期间,他担任多个研发项目负责人,带领团队3年内成功完成6颗SoC芯片的设计与流片工作。他与团队基于硬件构造语言搭建了OFDM通信SoC生成平台,完成了可重构OFDM基带处理器架构以及多个通信链路关键模块的生成器设计,可适配多种有线/无线OFDM通信协议,将通信链路从算法到硬件落地的周期缩短5倍以上。他作为第一发明人申请专利6项,其中1项获得授权,5项进入实质审查阶段,相关成果已在电网双模通信、电力计量等实际应用场景中落地。

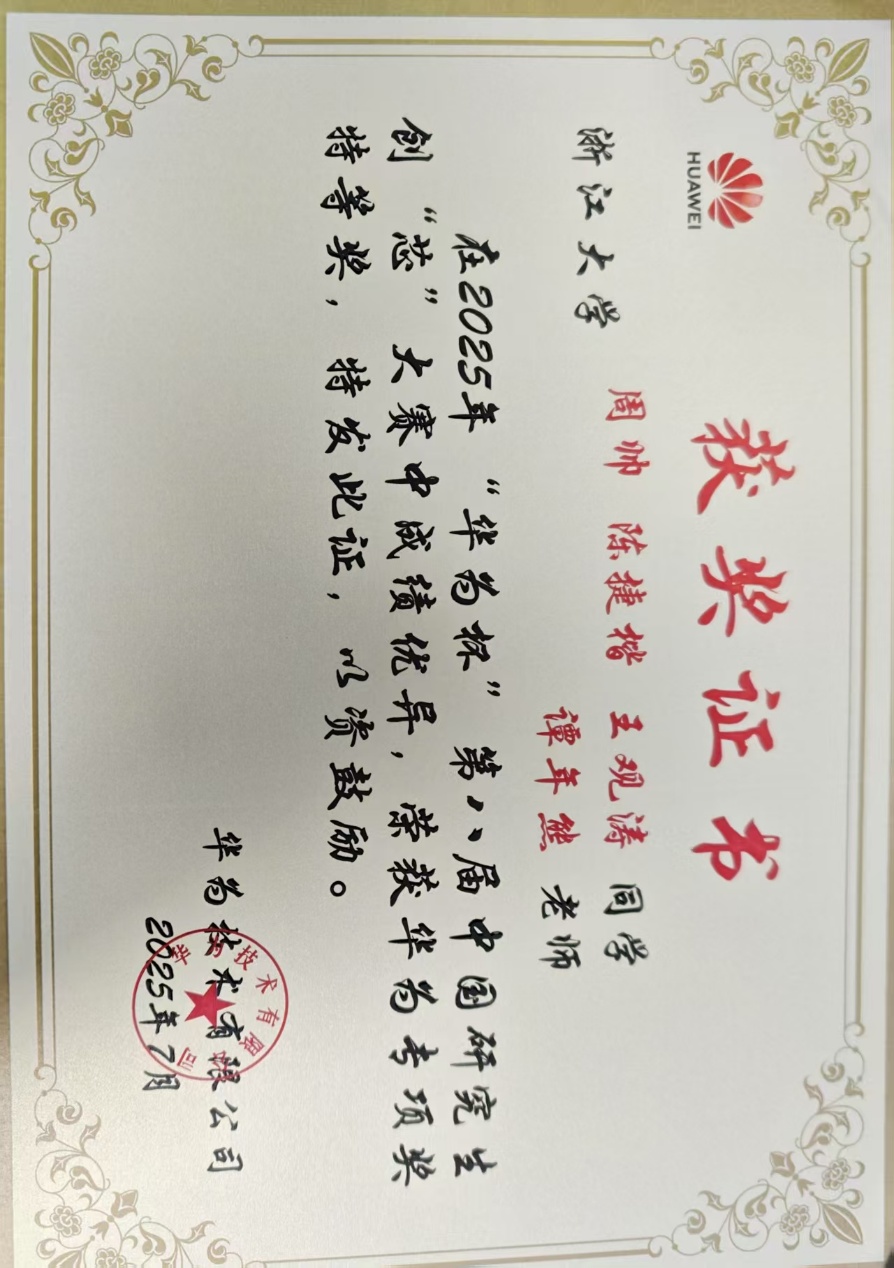

竞赛方面,他将这些设计理念应用于资源受限与多约束优化场景,并取得优秀成绩,先后获得全国大学生集成电路创新创业大赛全国一等奖、中国研究生创“芯”大赛全国一等奖和企业特等奖。在第七届全国大学生集成电路创新创业大赛中,周帅同学团队以音素识别与序列匹配相结合的方案,在极低资源下实现了 99.04% 的识别率,并通过片上内存优化与任务调度将延迟压缩至 13.7ms,同时显著降低功耗。在今年举办的第八届中国研究生创“芯”大赛中,他与团队构建了高度参数化的无线终端ICS 电路生成器,通过参数化并行度与流水线架构及设计空间探索实现了在特定约束下的最优硬件设计。

二、朋辈谈心

热爱让人甘愿投入,而投入会带来真正的成长。科研并不是每天都有突破,大多数时候我们都在调代码、改电路、跑仿真,像是在黑暗里摸索。但正是这些看似普通又重复的日常,让我们收获了深刻的理解和沉着的耐心。

生活偶有迷茫实属正常。遇到难题停下来沉淀,厚积薄发再走下一步,这是科研的节奏,也是生活的韵律。不要害怕慢,也不要害怕调整方向;只要保持好奇、保持热情,你就会发现自己正在悄悄变强。

愿学弟学妹们在未来的日子里,做自己热爱的事,走自己心仪的路,保持热情也多一份耐心,一切自会水到渠成。